Page 1

CYGNAL Integrated Products, Inc.

2002

9.2002; Rev. 1.2

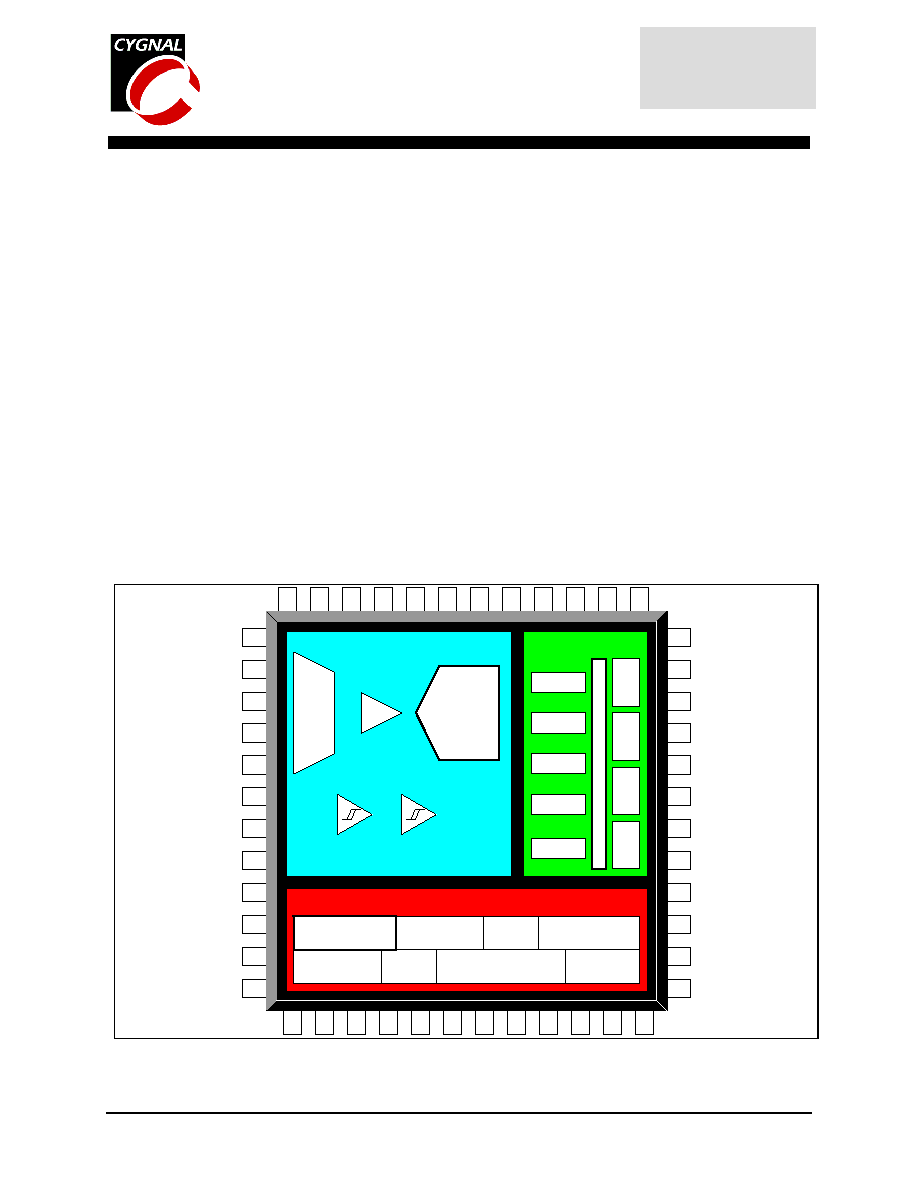

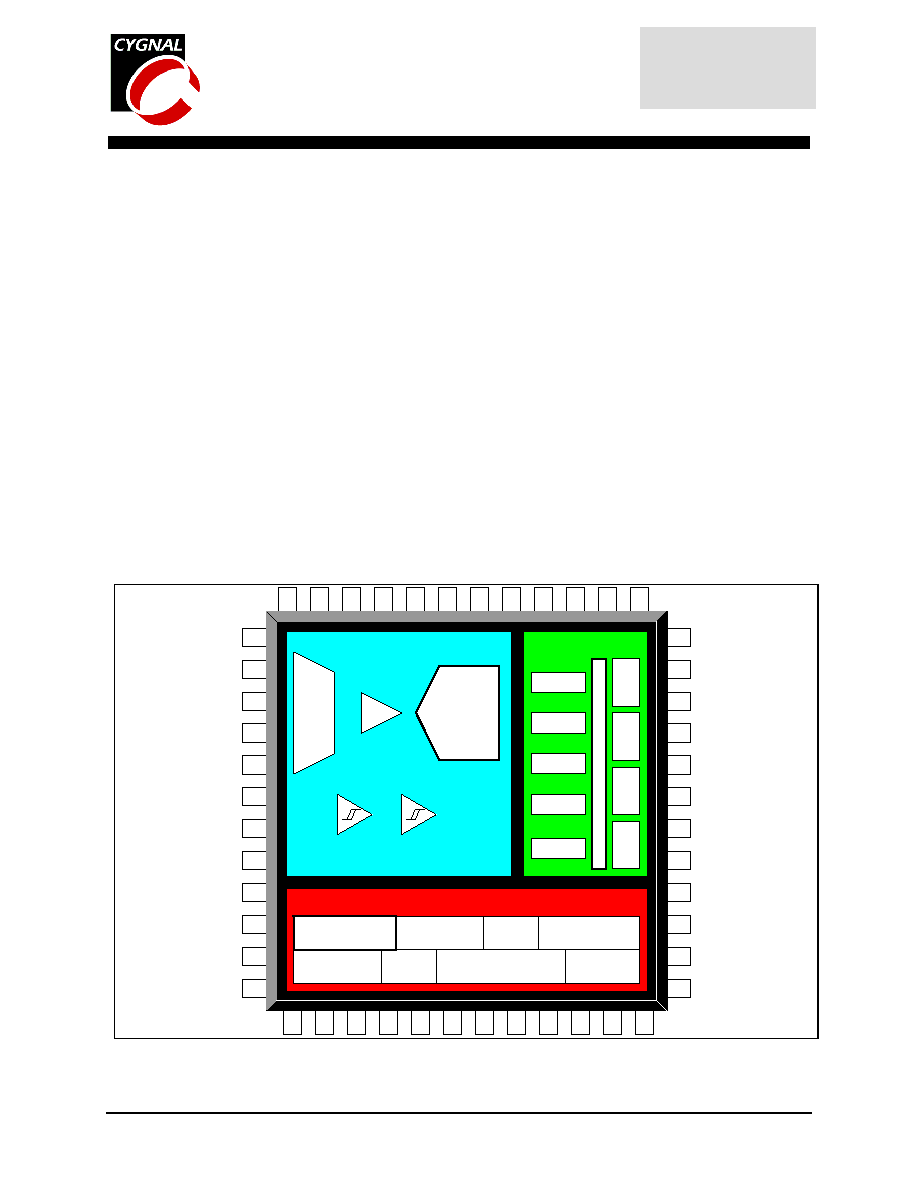

C8051F206

C8051F220/1/6

C8051F230/1/6

Mixed-Signal 8KB ISP FLASH MCU Family

JTAG

8K x 8

ISP FLASH

1280 x 8

SRAM

SANITY

CONTROL

+

-

SAR

ADC

CLOCK

CIRCUIT

PGA

AM

U

X

VOLTAGE

COMPARATORS

ANALOG PERIPHERALS

Port 0

Port 1

UART

SPI Bus

Port 2

Port 3

Di

g

i

t

a

l

M

U

X

Timer 0

Timer 1

Timer 2

DIGITAL I/O

HIGH-SPEED CONTROLLER CORE

EMULATION

CIRCUITRY

22 INTERRUPTS

8051 CPU

(25MIPS)

+

-

ANALOG PERIPHERALS

-

SAR ADC

� 12-bit Resolution (`F206)

� 8-Bit Resolution (`F220/1/6)

� �1/4 LSB INL (8-bit) and �2 LSB INL (12-bit)

� Up to 100ksps

� Up to 32 Channel Input Multiplexer; Each Port

I/O Pin can be an ADC Input

-

Two Comparators

� 16 Programmable Hysteresis States

� Configurable to Generate Interrupts or Reset

-

VDD Monitor and Brown-out Detector

ON-CHIP JTAG DEBUG

-

On-Chip Debug Circuitry Facilitates Full Speed, Non-

intrusive In-system Debug (No Emulator Required!)

-

Provides Breakpoints, Single-Stepping, Watchpoints,

Stack Monitor

-

Inspect/Modify Memory and Registers

-

Superior Performance to Emulation Systems Using

ICE-Chips, Target Pods, and Sockets

-

Complete, Low Cost Development Kit.

HIGH SPEED 8051

�

�

�

�C Core

-

Pipelined Instruction Architecture; Executes 70% of

Instructions in 1 or 2 System Clocks

-

Up to 25MIPS Throughput with 25MHz Clock

-

Expanded Interrupt Handler

MEMORY

-

256 Bytes Internal Data RAM

-

1024 Bytes XRAM (available on `F206/226/236)

-

8k Bytes FLASH; In-System Programmable in 512

byte Sectors

DIGITAL PERIPHERALS

-

Four byte wide Port I/O; All are 5V tolerant

-

Hardware UART and SPI bus

-

3 General Purpose 16-Bit Counter/Timers

-

Dedicated Watch-Dog Timer

-

Bi-directional Reset

-

System Clock: Internal Programmable Oscillator,

External Crystal, External RC, or External Clock

SUPPLY VOLTAGE .................2.7V to 3.6V

-

Typical Operating Current: 10mA @ 25MHz

-

Multiple Power Saving Sleep and Shutdown Modes

(48-Pin TQFP and 32-Pin LQFP Version Available)

Temperature Range: �40

�

�

�

�C to +85����C

Page 2

CYGNAL Integrated Products, Inc.

2002

9.2002; Rev. 1.2

C8051F206

C8051F220/1/6

C8051F230/1/6

TABLE OF CONTENTS

1. SYSTEM OVERVIEW ....................................................................................................... 6

Table 1.1.1. Product Selection Guide................................................................................................................ 6

Figure 1.1. C8051F206, C8051F220 and C8051F226 Block Diagram (48 TQFP) .......................................... 7

Figure 1.2 C8051F221 Block Diagram (32 LQFP)........................................................................................... 8

Figure 1.3 C8051F230 and C8051F236 Block Diagram (48 TQFP) ................................................................ 9

Figure 1.4 C8051F231 Block Diagram (32 LQFP)......................................................................................... 10

1.1.

CIP-51

TM

Microcontroller Core ............................................................................................................ 11

Figure 1.5. Comparison of Peak MCU Throughputs....................................................................................... 11

Figure 1.6. On-Board Clock and Reset ........................................................................................................... 12

1.2.

On-Board Memory ................................................................................................................................ 13

Figure 1.7. On-Board Memory Map ............................................................................................................... 13

1.3.

JTAG..................................................................................................................................................... 14

Figure 1.8. Debug Environment Diagram ....................................................................................................... 14

1.4.

Digital/Analog Configurable I/O........................................................................................................... 15

Figure 1.9. Port I/O Functional Block Diagram .............................................................................................. 15

1.5.

Serial Ports ............................................................................................................................................ 15

1.6.

Analog to Digital Converter .................................................................................................................. 16

Figure 1.10. ADC Diagram ............................................................................................................................. 16

1.7.

Comparators .......................................................................................................................................... 17

Figure 1.11. Comparator Diagram .................................................................................................................. 17

2. ABSOLUTE MAXIMUM RATINGS*............................................................................ 18

3. GLOBAL DC ELECTRICAL CHARACTERISTICS .................................................. 18

4. PINOUT AND PACKAGE DEFINITIONS.................................................................... 19

Table 4.1 Pin Definitions ................................................................................................................................ 19

Figure 4.1 TQFP-48 Pin Diagram.................................................................................................................... 21

Figure 4.2 LQFP-32 Pin Diagram .................................................................................................................... 22

Figure 4.3 TQFP-48 Package Drawing ............................................................................................................ 23

Figure 4.4 LQFP-32 Package Drawing ........................................................................................................... 24

5. ADC (8-Bit, C8051F220/1/6 Only).................................................................................... 25

Figure 5.1. 8-Bit ADC Functional Block Diagram.......................................................................................... 25

5.1.

Analog Multiplexer and PGA................................................................................................................ 25

5.2.

ADC Modes of Operation ..................................................................................................................... 25

Figure 5.2. 12-Bit ADC Track and Conversion Example Timing................................................................... 26

Figure 5.3. AMX0SL: AMUX Channel Select Register ................................................................................. 27

Figure 5.4. ADC0CF: ADC Configuration Register ....................................................................................... 28

Figure 5.5. ADC0CN: ADC Control Register (C8051F220/1/6 and C8051F206).......................................... 29

Figure 5.6. ADC0H: ADC Data Word Register (C8051F220/1/6 and C8051F206)...................................... 30

5.3.

ADC Programmable Window Detector................................................................................................. 30

Figure 5.7. ADC0GTH: ADC Greater-Than Data Register (C8051F220/1/6 and C8051F206) ..................... 30

Figure 5.8. ADC0LTH: ADC Less-Than Data Byte Register (C8051F220/1/6 and C8051F206).................. 30

Figure 5.9. 8-Bit ADC Window Interrupt Examples....................................................................................... 31

Table 5.1. 8-Bit ADC Electrical Characteristics ............................................................................................. 32

6. ADC (12-Bit, C8051F206 Only)........................................................................................ 33

Figure 6.1. 12-Bit ADC Functional Block Diagram........................................................................................ 33

6.1.

Analog Multiplexer and PGA................................................................................................................ 33

6.2.

ADC Modes of Operation ..................................................................................................................... 33

Figure 6.2. 12-Bit ADC Track and Conversion Example Timing................................................................... 34

Figure 6.3. AMX0SL: AMUX Channel Select Register ................................................................................. 35

Figure 6.4. ADC0CF: ADC Configuration Register (C8051F220/1/6 and C8051F206) ................................ 36

Figure 6.5. ADC0CN: ADC Control Register (C8051F220/1/6 and C8051F206).......................................... 37

Figure 6.6. ADC0H: ADC Data Word MSB Register (C8051F206) ............................................................. 38

Page 3

CYGNAL Integrated Products, Inc.

2002

9.2002; Rev. 1.2

C8051F206

C8051F220/1/6

C8051F230/1/6

Figure 6.7. ADC0L: ADC Data Word LSB Register (C8051F206)............................................................... 38

6.3.

ADC Programmable Window Detector................................................................................................. 38

Figure 6.8. ADC0GTH: ADC Greater-Than Data High Byte Register (C8051F206)..................................... 39

Figure 6.9. ADC0GTL: ADC Greater-Than Data Low Byte Register (C8051F206)...................................... 39

Figure 6.10. ADC0LTH: ADC Less-Than Data High Byte Register (C8051F206)........................................ 39

Figure 6.11. ADC0LTL: ADC Less-Than Data Low Byte Register (C8051F206)......................................... 39

Figure 6.12. 12-Bit ADC Window Interrupt Examples, Right Justified Data ................................................. 40

Figure 6.13. 12-Bit ADC Window Interrupt Examples, Left Justified Data ................................................... 41

Table 6.1. 12-Bit ADC Electrical Characteristics (C8015F206 only)............................................................. 42

7. VOLTAGE REFERENCE (C8051F206/220/221/226) ................................................... 43

Figure 7.1. Voltage Reference Functional Block Diagram ............................................................................. 43

Figure 7.2. REF0CN: Reference Control Register .......................................................................................... 44

Table 7.1. Reference Electrical Characteristics............................................................................................... 44

8. COMPARATORS.............................................................................................................. 45

Figure 8.1. Comparator Functional Block Diagram ........................................................................................ 45

Figure 8.2. Comparator Hysteresis Plot .......................................................................................................... 46

Figure 8.3. CPT0CN: Comparator 0 Control Register .................................................................................... 47

Figure 8.4. CPT1CN: Comparator 1 Control Register .................................................................................... 48

Table 8.1. Comparator Electrical Characteristics............................................................................................ 49

9. CIP-51 MICROCONTROLLER ..................................................................................... 50

Figure 9.1. CIP-51 Block Diagram ................................................................................................................. 50

9.1.

INSTRUCTION SET ............................................................................................................................ 52

Table 9.1. CIP-51 Instruction Set Summary.................................................................................................... 52

9.2.

MEMORY ORGANIZATION.............................................................................................................. 56

Figure 9.2. Memory Map ................................................................................................................................ 57

9.3.

SPECIAL FUNCTION REGISTERS ................................................................................................... 59

Table 9.2. Special Function Register Memory Map........................................................................................ 59

Table 9.3. Special Function Registers............................................................................................................. 59

Figure 9.3. SP: Stack Pointer .......................................................................................................................... 62

Figure 9.4. DPL: Data Pointer Low Byte ........................................................................................................ 62

Figure 9.5. DPH: Data Pointer High Byte....................................................................................................... 62

Figure 9.6. PSW: Program Status Word ......................................................................................................... 63

Figure 9.7. ACC: Accumulator ....................................................................................................................... 64

Figure 9.8. B: B Register................................................................................................................................. 64

9.4.

INTERRUPT HANDLER..................................................................................................................... 65

Figure 9.9. SWCINT: Software Controlled Interrupt Register........................................................................ 66

Table 9.4. Interrupt Summary ......................................................................................................................... 66

Figure 9.10. IE: Interrupt Enable .................................................................................................................... 68

Figure 9.11. IP: Interrupt Priority ................................................................................................................... 69

Figure 9.12. EIE1: Extended Interrupt Enable 1 ............................................................................................. 70

Figure 9.13. EIE2: Extended Interrupt Enable 2 ............................................................................................. 71

Figure 9.14. EIP1: Extended Interrupt Priority 1 ............................................................................................ 72

Figure 9.15. EIP2: Extended Interrupt Priority 2 ............................................................................................ 73

9.5.

Power Management Modes ................................................................................................................... 74

Figure 9.16. PCON: Power Control Register .................................................................................................. 75

10. FLASH MEMORY............................................................................................................ 76

10.1.

Programming The Flash Memory...................................................................................................... 76

Table 10.1. FLASH Memory Electrical Characteristics.................................................................................. 76

Non-volatile Data Storage................................................................................................................................ 77

10.2.

Security Options................................................................................................................................ 77

Figure 10.1. Flash Program Memory Security Bytes ....................................................................................... 78

Figure 10.2. PSCTL: Program Store RW Control........................................................................................... 79

Figure 10.3. FLSCL: Flash Memory Timing Prescaler ................................................................................... 80

Figure 10.4. FLACL: Flash Access Limit ....................................................................................................... 80

Page 4

CYGNAL Integrated Products, Inc.

2002

9.2002; Rev. 1.2

C8051F206

C8051F220/1/6

C8051F230/1/6

11. ON-CHIP XRAM (C8051F206/226/236) ......................................................................... 81

Figure 11.1. EMI0CN: External Memory Interface Control ........................................................................... 81

12. RESET SOURCES ............................................................................................................ 82

Figure 12.1. Reset Sources Diagram ............................................................................................................... 82

12.1.

Power-on Reset ................................................................................................................................. 83

12.2.

Software Forced Reset....................................................................................................................... 83

Figure 12.2. VDD Monitor Timing Diagram .................................................................................................. 83

12.3.

Power-fail Reset ................................................................................................................................ 83

12.4.

External Reset ................................................................................................................................... 84

12.5.

Missing Clock Detector Reset ........................................................................................................... 84

12.6.

Comparator 0 Reset........................................................................................................................... 84

12.7.

Watchdog Timer Reset...................................................................................................................... 84

Figure 12.3. WDTCN: Watchdog Timer Control Register ............................................................................. 85

Figure 12.4. RSTSRC: Reset Source Register ................................................................................................ 86

Table 12.1. VDD Monitor Electrical Characteristics ...................................................................................... 87

13. OSCILLATOR................................................................................................................... 88

Figure 13.1. Oscillator Diagram...................................................................................................................... 88

Figure 13.2. OSCICN: Internal Oscillator Control Register ........................................................................... 89

Table 13.1. Internal Oscillator Electrical Characteristics................................................................................ 89

Figure 13.3. OSCXCN: External Oscillator Control Register......................................................................... 90

13.1.

External Crystal Example.................................................................................................................. 91

13.2.

External RC Example........................................................................................................................ 91

13.3.

External Capacitor Example.............................................................................................................. 91

14. PORT INPUT/OUTPUT ................................................................................................... 92

14.1.

Port I/O Initialization ........................................................................................................................ 92

Figure 14.1. Port I/O Functional Block Diagram ............................................................................................ 93

Figure 14.2. Port I/O Cell Block Diagram ...................................................................................................... 93

Figure 14.3. PRT0MX: Port I/O MUX Register 0 .......................................................................................... 94

Figure 14.4. PRT1MX: Port I/O MUX Register 1 .......................................................................................... 95

Figure 14.5. PRT2MX: Port I/O MUX Register 2 .......................................................................................... 95

14.2.

General Purpose Port I/O .................................................................................................................. 96

Figure 14.6. P0: Port0 Register ....................................................................................................................... 96

Figure 14.7. PRT0CF: Port0 Configuration Register ...................................................................................... 96

Figure 14.8. P0MODE: Port0 Digital/Analog Input Mode ............................................................................. 97

Figure 14.9. P1: Port1 Register ....................................................................................................................... 97

Figure 14.10. PRT1CF: Port1 Configuration Register .................................................................................... 97

Figure 14.11. P1MODE: Port1 Digital/Analog Input Mode ........................................................................... 98

Figure 14.12. P2: Port2 Register ..................................................................................................................... 98

Figure 14.13. PRT2CF: Port2 Configuration Register .................................................................................... 98

Figure 14.14. P2MODE: Port2 Digital/Analog Input Mode ........................................................................... 99

Figure 14.15. P3: Port3 Register* ................................................................................................................... 99

Figure 14.16. PRT3CF: Port3 Configuration Register* .................................................................................. 99

Figure 14.17. P3MODE: Port3 Digital/Analog Input Mode* ....................................................................... 100

Table 14.1. Port I/O DC Electrical Characteristics ....................................................................................... 100

15. SERIAL PERIPHERAL INTERFACE BUS................................................................ 101

Figure 15.1. SPI Block Diagram ................................................................................................................... 101

Figure 15.2. Typical SPI Interconnection ..................................................................................................... 102

15.1.

Signal Descriptions ......................................................................................................................... 102

15.2.

Operation......................................................................................................................................... 103

Figure 15.3. Full Duplex Operation .............................................................................................................. 103

15.3.

Serial Clock Timing ........................................................................................................................ 104

Figure 15.4. Data/Clock Timing Diagram..................................................................................................... 104

15.4.

SPI Special Function Registers ....................................................................................................... 105

Figure 15.5. SPI0CFG: SPI Configuration Register...................................................................................... 105

Page 5

CYGNAL Integrated Products, Inc.

2002

9.2002; Rev. 1.2

C8051F206

C8051F220/1/6

C8051F230/1/6

Figure 15.6. SPI0CN: SPI Control Register.................................................................................................. 106

Figure 15.7. SPI0CKR: SPI Clock Rate Register.......................................................................................... 107

Figure 15.8. SPI0DAT: SPI Data Register.................................................................................................... 107

16. UART ................................................................................................................................ 108

Figure 16.1. UART Block Diagram .............................................................................................................. 108

16.1.

UART Operational Modes .............................................................................................................. 109

Table 16.1. UART Modes............................................................................................................................. 109

Figure 16.2. UART Mode 0 Interconnect ..................................................................................................... 109

Figure 16.3. UART Mode 0 Timing Diagram............................................................................................... 109

Figure 16.4. UART Mode 1 Timing Diagram............................................................................................... 110

Figure 16.5. UART Modes 1, 2, and 3 Interconnect Diagram ...................................................................... 111

Figure 16.6. UART Modes 2 and 3 Timing Diagram ................................................................................... 111

16.2.

Multiprocessor Communications..................................................................................................... 112

Figure 16.7. UART Multi-Processor Mode Interconnect Diagram............................................................... 112

Table 16.2. Oscillator Frequencies for Standard Baud Rates........................................................................ 113

Figure 16.8. SBUF: Serial (UART) Data Buffer Register............................................................................. 113

Figure 16.9. SCON: Serial Port Control Register ......................................................................................... 114

17. TIMERS............................................................................................................................ 115

17.1.

Timer 0 and Timer 1 ....................................................................................................................... 115

Figure 17.1. T0 Mode 0 Block Diagram ....................................................................................................... 116

Figure 17.2. T0 Mode 2 Block Diagram ....................................................................................................... 117

Figure 17.3. T0 Mode 3 Block Diagram ....................................................................................................... 118

Figure 17.4. TCON: Timer Control Register ................................................................................................ 119

Figure 17.5. TMOD: Timer Mode Register .................................................................................................. 120

Figure 17.6. CKCON: Clock Control Register.............................................................................................. 121

Figure 17.7. TL0: Timer 0 Low Byte............................................................................................................ 122

Figure 17.8. TL1: Timer 1 Low Byte............................................................................................................ 122

Figure 17.9. TH0: Timer 0 High Byte........................................................................................................... 122

Figure 17.10. TH1: Timer 1 High Byte......................................................................................................... 122

17.2.

Timer 2............................................................................................................................................ 123

Figure 17.11. T2 Mode 0 Block Diagram ..................................................................................................... 124

Figure 17.12. T2 Mode 1 Block Diagram ..................................................................................................... 125

Figure 17.13. T2 Mode 2 Block Diagram ..................................................................................................... 126

Figure 17.14. T2CON: Timer 2 Control Register ......................................................................................... 127

Figure 17.15. RCAP2L: Timer 2 Capture Register Low Byte ...................................................................... 128

Figure 17.16. RCAP2H: Timer 2 Capture Register High Byte ..................................................................... 128

Figure 17.17. TL2: Timer 2 Low Byte.......................................................................................................... 128

Figure 17.18. TH2: Timer 2 High Byte......................................................................................................... 128

18. JTAG................................................................................................................................. 129

Figure 18.1. IR: JTAG Instruction Register .................................................................................................. 129

18.1.

Flash Programming Commands....................................................................................................... 130

Figure 18.2 FLASHCON: JTAG Flash Control Register.............................................................................. 131

Figure 18.3. FLASHADR: JTAG Flash Address Register ............................................................................. 131

Figure 18.4. FLASHDAT: JTAG Flash Data Register.................................................................................. 132

Figure 18.5. FLASHSCL: JTAG Flash Scale Register ................................................................................. 132

18.2.

Boundary Scan Bypass and ID Code............................................................................................... 133

Figure 18.6. DEVICEID: JTAG Device ID Register .................................................................................... 133

18.3.

Debug Support ................................................................................................................................ 133